Multichannel PWM FPGA code

$2-20 USD / hour

In Progress

Posted over 10 years ago

$2-20 USD / hour

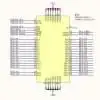

Create a set of Verilog or VHDL modules for a FPGA that will generate multiple channels of PWM digital outputs. Frequency of the PWMs should be as high as possible so it should equal the FPGA operating frequency. Number of channels and number of bits used to represent the duty cycle percentage must be configurable at compile / synthesis time. We expect channel count to be 32 and number of bits to be 10. The duty percent value of each channel would be communicated by external microcontroller over a simple serial or parallel bus.

Some guidance over selection of FPGA and pin layout will be required.

Project ID: 5034005

About the project

26 proposals

Remote project

Active 10 yrs ago

Looking to make some money?

Benefits of bidding on Freelancer

Set your budget and timeframe

Get paid for your work

Outline your proposal

It's free to sign up and bid on jobs

26 freelancers are bidding on average $13 USD/hour for this job

6.8

6.8

2.4

2.4

2.2

2.2

2.1

2.1

1.6

1.6

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

0.0

About the client

Ljubljana, Slovenia

3

Payment method verified

Member since Oct 16, 2013

Client Verification

Other jobs from this client

€30-250 EUR

€50-200 EUR

€8-30 EUR

€30-250 EUR

€30-250 EUR

Similar jobs

$250-750 USD

$15-25 USD / hour

£2-5 GBP / hour

$250-750 NZD

$30-250 USD

£18-36 GBP / hour

$250-750 USD

$10-20 USD

$30-250 USD

$250-750 USD

$30-250 USD

₹600-1500 INR

€30-250 EUR

₹1500-12500 INR

₹100-400 INR / hour

₹400-750 INR / hour

₹1500-12500 INR

$250-750 USD

€18-36 EUR / hour

$250-750 USD

Thanks! We’ve emailed you a link to claim your free credit.

Something went wrong while sending your email. Please try again.

Loading preview

Permission granted for Geolocation.

Your login session has expired and you have been logged out. Please log in again.